ELSEVIER

Contents lists available at ScienceDirect

# Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

## A 30 V rail-to-rail operational amplifier

Chua-Chin Wang\*, Tsung-Yi Tsai, Wen-Je Lu, Chih-Lin Chen, Yi-Lun Wu

National Sun Yat-Sen University, Department of Electrical Engineering, 70 Lian-Hai Road, Kaohsiung, Taiwan

#### ARTICLE INFO

Article history:

Received 19 December 2014

Received in revised form

15 May 2015

Accepted 26 June 2015

Available online 24 August 2015

Keywords:

High voltage

Operational amplifier

High voltage transceiver

BCD process

#### ABSTRACT

This work presents a high-voltage (HV) operational amplifier (OPA). OPAs are widely used in signal conditioning circuits for industrial applications and integrated circuits (ICs). Particularly, in HV applications like BMS (battery management system), the signal conditioning circuits are always used to transfer voltage signal between HV domain and low voltage (LV) domain. Notably, the voltage from the HV domain could be as high as tens of volts, which might cause damages to regular silicon-based transistors. Nevertheless, since the resolution of the signal conditioning circuits depends on the output range and the operation range is determined by the input range, the input and output ranges of the signal conditioning circuits have been a key issue in the HV applications. We propose a rail-to-rail HV OPA to resolve these issues. The proposed design is implemented using 0.25  $\mu$ m 1-poly 3-metal 60 V BCD process. The core area is  $0.809 \times 0.303 \text{ mm}^2$ . DC gain and unit-gain bandwidth of the proposed rail-to-rail HV OPA are measured to be 41 dB and 0.3 MHz, respectively. Finally, the proposed rail-to-rail HV OPA is proven on silicon to receive any signals between 0 and 30 V and transmit a signal in the range of [0.4, 29.6] V.

© 2015 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Electric vehicle (EV) has been recognized as a key role in the energy-shortage future. EV battery modules provide electrical energy to drive everything, including motors [1]. The battery modules of EVs have to generate outputs with tens of volts. Traditional EV BMS usually uses a monitoring integrated circuit (IC) to carry out battery module monitoring, battery module protection, and charge equalization [1–3]. Thus, the battery signal transfer devices must attain wide input and output ranges to meet such a demand. The input and output ranges of the battery signal transfer devices are determined by operational amplifiers (OPAs) of these ICs. Wide input and output ranges up to tens of volts result in difficulties of OPA design in these kinds of applications.

OPAs are widely used in signal transfer devices such as the adder, subtractor, and analog-to-digital converter (ADC) [1–8]. Many prior OPAs relied on high gain to reduce the gain error [4–6]. In [6], a high gain OPA was proposed. However, the performance of the OPA is affected by process variation [7,8]. Thus, the constant-gm designs were also proposed to reduce process variation [7,8].

Since the input and output ranges of OPA directly determine the operating range of the HV signal transfer performance, rail-to-rail OPAs are widely used to resolve these problems [9-19]. Many lowvoltage (LV) rail-to-rail OPAs were proposed [9-19]. An LV operational transconductance amplifier (OTA) was proposed [10], where the output current versus the input voltage is linearized for a differential input voltage range extended from rail-to-rail. Three compact CMOS voltage-to-current converters based on OTA/common-source configurations were also reported [11], which attain rail-to-rail input and output ranges. A laser-trimmed rail-to-rail OPA with integrated laser-trimmable polysilicon resistors was disclosed to reduce the input offset voltage mismatch [15]. However, these LV designs cannot be used in HV devices, e.g., 30 V range, [4–19]. Thus, HV OPAs were proposed using HV devices [20-24]. A 36-V [FET-input bipolar OPA was implemented using SOI SiGe bipolar process [20]. The cost of the SOI process is much more expensive than standard high voltage CMOS process [20,21]. Lemkin et al. proposed a 200-V HV amplifier, which is implemented using 10-V trench-isolated CMOS process, but the input range is only 8 V [22]. The input range of the many prior HV OPAs is limited in low voltage range, which means the HV OPAs cannot be used in wide range HV applications [20-24].

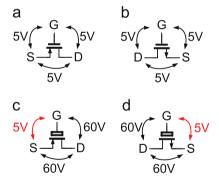

In this study, we propose a rail-to-rail HV OPA, which is implemented using a 0.25  $\mu m$  1-poly 3-metal 60 V BCD process. The voltage limitation of the LV PMOS and LV NMOS is 5 V between any two terminals, as shown in Fig. 1(a) and (b), respectively. By contrast, the voltage constraints of HV PMOS and

<sup>\*</sup> Corresponding author. Tel.: +886 7 5252000x4144; fax: +886 7 5254199. E-mail addresses: ccwang@ee.nsysu.edu.tw (C.-C. Wang), zack@vlsi.ee.nsysu.edu.tw (T.-Y. Tsai), wen@vlsi.ee.nsysu.edu.tw (W.-J. Lu), clchen@vlsi.ee.nsysu.edu.tw (C.-L. Chen), helen2924@vlsi.ee.nsysu.edu.tw (Y.-L. Wu).

HV NMOS are different, as shown in Fig. 1(c) and (d), respectively. Notably,  $V_{GS}$  of the HV PMOS and HV NMOS must be lower than 5 V to prevent hazards. The proposed rail-to-rail HV OPA attains wide input and output ranges, namely attain 0–30 V and 0.4–29.6 V, respectively, given that the supply voltage is 30 V.

### 2. Architecture of the proposed HV OPA design

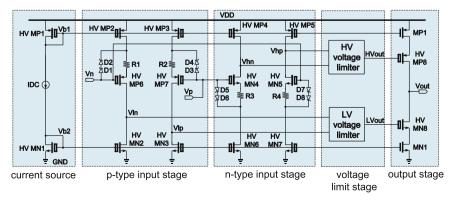

Fig. 2 shows the block diagram of the proposed rail-to-rail HV OPA consisting of 5 major blocks, i.e., a current source, a p-type input stage, an n-type input stage, a voltage limit stage, and an output stage. The proposed rail-to-rail HV OPA uses a p-type input stage and an n-type input stage to achieve a rail-to-rail input range. The output stage also provides a wide voltage range. However, wide input and output ranges must take over-voltage problems into consideration. Zener diodes and voltage limit stages are used to provide protection against the over-voltage problems in our design. The details of these function blocks are given in the following text.

#### 2.1. n-Type input stage

As addressed earlier,  $V_{\rm GS}$  of the HV MOSs must be limited lower than 5 V, but the VDD and input voltage might be 30 V and 0–30 V, respectively. Conventional LV OPA, therefore, cannot be directly migrated to be HV OPA. Thus, the zener diodes are used to clamp  $V_{\rm GS}$  of the HV MOSs under 5 V. Notably, the n-well resistor is used to reduce channel length modulation effect of the HV MOSs.

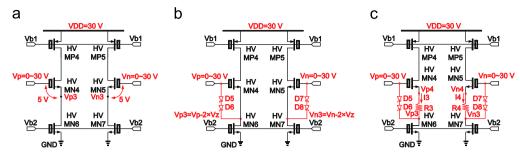

Referring to Fig. 3(a), an n-type input stage directly migrated by an LV OPA is shown, where the voltage ranges of the Vp and Vn are 0–30 V. Thus, the V<sub>GS</sub>'s of HV MN4 and HV NM5 easily exceed 5 V to destroy the devices.

Fig. 1. Schematic of the (a) LV PMOS, (b) LV NMOS, (c) HV PMOS, and (d) HV NMOS.

• If four zener diodes are used to clamp the D–G voltage drop of HV MN4 and HV NM5, as shown in Fig. 3(b), Vn3 and Vp3 become Vn $-2 \times$  Vz and Vn $-2 \times$  Vz, respectively, where Vz is the forward bias voltage of the zener diodes. Thus,  $V_{GS}$ 's of HV MN4 and HV NM5 are clamped to be  $2 \times$  Vz and  $2 \times$  Vz, respectively. Though the problem of  $V_{GS}$  constraint is resolved,  $V_{DS}$ 's of HV MN6 and HV MN7 always drift with different input voltages. The major reason is that the channel length modulation effect becomes very serious based on Eq. (1), when the  $V_{DS}$  is not a constant.

$$I_{\text{sat}} = \frac{1}{2} u C_{\text{ox}} \frac{W}{L} (V_{\text{GS}} - \text{Vth})^2 (1 + \lambda V_{\text{DS}})$$

(1)

where  $I_{\rm sat}$  is the saturation current, W is the channel width, L is the channel length,  $C_{\rm ox}$  is the oxide capacitance, u is the mobility,  $V_{\rm DS}$  is the voltage difference between drain and source of MOS,  $\lambda$  is the channel length modulation coefficient, and Vth is the threshold voltage.

- To resolve the channel modulation problem, two n-well resistors are added at the source of HV MN4 and HV MN5, respectively, as shown in Fig. 3(c), to reduce *V*<sub>DS</sub> drop.

- Vp3 and Vn3 then become as  $I3 \times R3 + (Vn 2 \times Vz)$  and  $I4 \times R4 + (Vn 2 \times Vz)$ , respectively, which make  $V_{GS}$  of HV MN4 and HV MN5 vary with the input voltage.

- Thus, the currents of HV MN4, HV NM5, HV MN6, and HV NM7 will be kept constant regardless of different input voltages.

In summary, by the insertion of the zener diodes and n-well resistors, the proposed n-type stage not only attains HV input range, it also avoids the over-voltage problem and reduce the channel length modulation effect.

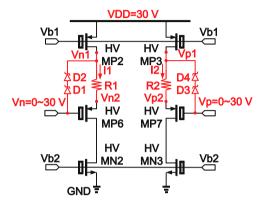

#### 2.2. p-Type input stage

By a similar thought, the p-type input stage is considered as the dual design of the n-type counter part. The proposed p-type input stage is shown in Fig. 4.

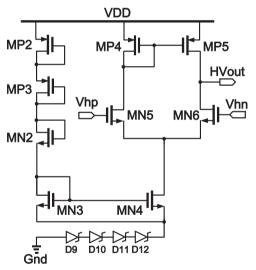

#### 2.3. HV voltage limiter

The HV voltage limiter composed of 4 PMOSs, 5 NMOSs, and 4 zener diodes is shown in Fig. 5. HVout is constrained in a high voltage range, which is written as

$$HVlow \le HVout \le HVhigh$$

(2)

where HVlow is  $V_{DS-MN6} + V_{DS-MN4} + 4 \times Vz'$ , HVhigh is  $VDD - V_{SD-MP5}$ , Vz' is reverse bias voltage of the zener diodes. Notably, HVout is the gate drive of HV MP8 in Fig. 2. Besides, the gate drive of the MP1 is mirrored from the current source block, as

Fig. 2. Schematic of the proposed rail-to-rail HV OPA.

Fig. 3. Schematics of different n-type input stages (a) without 2 n-well resistors and 4 zener diodes, (b) without 2 n-well resistors, and (c) the proposed design.

Fig. 4. Schematic of the proposed p-type input stage.

Fig. 5. Schematic of the HV voltage limiter.

shown in Fig. 2. Since the gate drive of HV MP8 is clamped, the output stage will not run into the over-voltage problem.

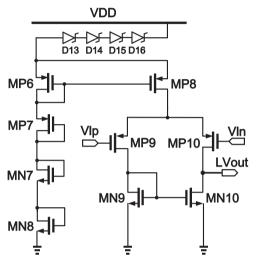

## 2.4. LV voltage limiter

The counter part of the HV limiter is the LV voltage limiter composed of 4 PMOSs, 5 NMOSs, and 4 zener diodes, as shown in Fig. 6:

$$LVlow \le LVout \le LVhigh$$

(3)

where LVhigh is VDD $-4 \times Vz' - V_{SD-MP8} - V_{SD-MP10}$ , LVlow is  $V_{DS-MN10}$ . Similarly, because the gate drive of HV MN8 in Fig. 2 is clamped as shown in Eq. (3) and the gate drive of MN1 is also mirrored from the current source block, they will not encounter any over-voltage hazard, either.

Fig. 6. Schematic of the LV voltage limiter.

#### 2.5. Transfer function analysis

The small signal analysis of the rail-to-rail HV OPA is defined in Eqs. (4) and (5), when the p-type input stage is solely activated. Notably, the analysis of the n-type input stage operation is similar.

$$Av(s), p \approx \frac{A_{DC}, p \times (1 + w_{z1} \times s)}{(1 + w_{p1} \times s) \times (1 + w_{p2} \times s) \times (1 + w_{p3} \times s)}$$

(4)

$A_{\rm DC}, p \approx g_{\rm m,HV~MP6}$

$$\times \left(g_{\text{m,HV MP8}} \times r_{\text{o,HV MP8}} \times r_{\text{o,MP1}} + r_{\text{o,HV MP8}} + r_{\text{o,MP1}}\right) \tag{5}$$

where  $A_{\rm DC}$ , p is the DC gain,  $w_{\rm z1}$  is the first zero of the p-type input stage,  $w_{\rm p1}$  is the first pole of the p-type input stage,  $w_{\rm p2}$  is the first pole of the LV voltage limiter,  $w_{\rm p3}$  is the first pole of the output stage, and the  $g_{\rm m,[X]}$  and  $r_{\rm o,[X]}$  denote the transconductance and the output resistance, respectively. (The [X] is the name of the MOS.) Thus, the Av(s), p can be written as

$$Av(s), p \approx \frac{A_{DC}, p \times \left(1 + \frac{1}{r_{o,HV MP6} \times C_{gd,HV MP6}} \times s\right)}{\left(1 + \frac{r_{o,HV MP6} \|r_{o,HV MP6}\|}{C_{tot1} \times C_{gd,HV MP6}} \times s\right) \left(1 + \frac{1}{R_{tot2} \times C_{tot2}} \times s\right) \left(1 + \frac{1}{R_{tot3} \times C_{tot3}} \times s\right)}$$

$$(6)$$

where  $C_{\rm gd,HV~MP6}$  is the capacitance between gate and drain of HV MP6,  $C_{\rm tot1}$  is the overall output capacitance of the p-type input stage,  $R_{\rm tot2}$  is the overall output resistance,  $C_{\rm tot2}$  is the capacitance of the LV voltage limiter,  $C_{\rm tot3}$  is the overall output capacitance of the output stage, and  $R_{\rm tot3}$  is shown as below:

$$R_{\text{tot3}} = (g_{\text{m.HV MP8}} \times r_{\text{o.HV MP8}} \times r_{\text{o.MP1}} + r_{\text{o.HV MP8}} + r_{\text{o.MP1}})$$

(7)

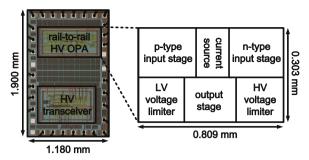

Fig. 7. Die photo of the proposed rail-to-rail HV OPA and HV transceiver.

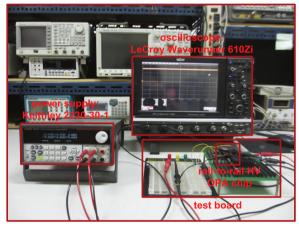

### measurement site

Fig. 8. Measurement site of this work.

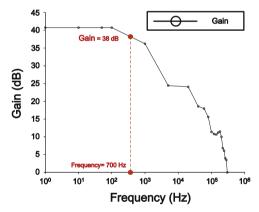

Fig. 9. Frequency response of the rail-to-rail HV OPA.

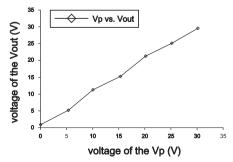

Fig. 10. Measured DC sweep of the proposed rail-to-rail HV OPA.

Table 1

Comparison between the proposed design and prior works.

|                    | [20]             | [21]         | This work   |

|--------------------|------------------|--------------|-------------|

| Year               | 2011             | 2012         | 2014        |

| Process (µm)       | SOI SiGe bipolar | BCD6 SOI     | 0.25 µm BCD |

| Supply voltage (V) | 40               | ± 50         | 30          |

| DC gain (dB)       | N/A              | 40.9         | 41.0        |

| GBW (MHz)          | 11               | 6.5          | 0.3         |

| SR (V/µs)          | 20               | 1800         | 4.78        |

| Average power (mW) | 72               | 37           | 30          |

| ICMR (V)           | N/A              | -3.5 to +3.5 | 0–30        |

| Output swing (V)   | N/A              | 90 (pk-pk)   | 0.4–29.6    |

| Area (mm²)         | 2.1              | 3.2          | 0.245       |

#### 3. Implementation and measurement results

The proposed design is implemented using the 0.25  $\mu$ m 1-poly 3-metal 60 V BCD process. Fig. 7 shows the die photo of the proposed rail-to-rail HV OPA and a HV transceiver, where the core area of the proposed rail-to-rail HV OPA is  $0.809 \times 0.303 \text{ mm}^2$ . The measurement environment of this work is shown in Fig. 8. Fig. 9 shows the frequency response of the proposed rail-to-rail HV OPA, which is configured as a unit-gain buffer. DC gain and unit-gain bandwidth of the proposed HV OPA are 41 dB and 0.3 MHz, respectively. Besides, the -3 dB bandwidth is 0.07 MHz. Fig. 10 shows the DC sweep of the proposed rail-to-rail HV OPA. Notably, this design is meant to be a HV and LV interface, wide input and output ranges are top priority. Table 1 shows the comparison between the proposed rail-to-rail HV OPA design and several prior works. Notably, our design attains the widest input range, the best DC gain, the smallest power, and the smallest area.

## 4. Conclusion

In this paper, we propose a rail-to-rail HV OPA, which is physically implemented using a typical 0.25  $\mu m$  1-poly 3-metal 60 V BCD process. The on-silicon measurement results justify that the proposed rail-to-rail HV OPA attains rail-to-rail input range (0–30 V) and wide output ranges (0.4–29.6 V). Notably, our design attains the widest input range, the smallest area, and the lowest average power compared with the prior works.

#### Acknowledgement

It was also partially supported by National Science Council, Taiwan, under Grants NSC101-3113-P-110-004, NSC102-2221-E-110-081-MY3, and NSC102-3113-P-110-010. The authors would like to express their deepest gratefulness to CIC (Chip Implementation Center) of NARL (Nation Applied Research Laboratories), Taiwan, for their thoughtful chip fabrication service.

#### References

- C.-H. Kim, M.-Y. Kim, G.-W. Moon, A modularized charge equalizer using a battery monitoring IC for series-connected Li-ion battery strings in electric vehicles, IEEE Trans. Power Electron. 28 (August (8)) (2013) 3779–3787.

- [2] INA212-Q1 Datasheet, Texas Instruments, Dallas, TX, 2013.

- [3] Bp78PL114 Datasheet, Texas Instruments, Dallas, TX, 2008.

- [4] X. Yuan, Y. Wang, Y. Li, A high gain, power efficient two-stage amplifier with recycling telescopic input stage, in: Proceedings of the 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, October 2012, pp. 1–3.

- [5] E. Kamrani, A. Sultana, M. Sawan, Tunable, low-power, high-gain transimpedance amplifier for fNIRS photoreceiver front-end, in: Proceedings of the 2011 IEEE 54th International Midwest Symposium on Circuits and Systems, August 2011, pp. 1–4.

- [6] G. Maiellaro, E. Ragonese, A. Castorina, S. Jacob, M. Benwadih, R. Coppard, E. Cantatore, G. Palmisano, High-gain operational transconductance amplifiers in a printed complementary organic TFT technology on flexible foil, IEEE Trans. Circuits Syst. I, Regular Pap. 60 (December (12)) (2013) 3117–3125.

- [7] T.-S. Mohammad, A.-A. Hamoui, A 1-V process-insensitive current-scalable two-stage opamp with enhanced dc gain and settling behavior in 65-nm digital CMOS, IEEE J. Solid-State Circuits 48 (March (3)) (2011) 660-668.

- [8] S.J.G. Gift, B. Maundy, Improving the bandwidth gain-independence and accuracy, IEEE Trans. Circuits Syst. II, Express Briefs 52 (March (3)) (2005)

- [9] S.-R. Zarabadi, F. Larsen, M. Ismail, A reconfigurable op-amp/DDA CMOS amplifier architecture, IEEE Trans. Circuits Syst. I, Regular Pap. 39 (June (6)) (1992) 484–487.

- [10] M.-F. Li, U. Dasgupta, X.-W. Zhang, Y.-C. Lim, A low-voltage CMOS OTA with rail-to-rail differential input range, IEEE Trans. Circuits Syst. I, Regular Pap. 47 (January (1)) (2000) 1–8.

- [11] C. Azcona, B. Calvo, S. Celma, N. Medrano, P.-A. Martinez, Low-voltage low-power CMOS rail-to-rail voltage-to-current converters, IEEE Trans. Circuits Syst. I, Regular Pap. 60 (September (9)) (2013) 2333–2342.

- [12] L.H.C. Ferreira, T.-C. Pimenta, R.-L. Moreno, An ultra-low-voltage ultra-low-power CMOS Miller OTA with rail-to-rail input/output swing, IEEE Trans. Circuits Syst. II, Express Briefs 54 (October (10)) (2007) 843–847.

- [13] R.-A. Jaime, M.-S. Sawant, S. Thoutam, J.L.M. Antonio, R.G. Carvajal, New low-voltage class AB/AB CMOS op amp with rail-to-rail input/output swing, IEEE Trans. Circuits Syst. II, Express Briefs 53 (April (4)) (2006) 289–293.

- [14] T. Song, J. Hu, X. Li, S. Yan, A constant-gm constant-slew-rate rail-to-rail input stage with static feedback and dynamic current steering for VLSI cell libraries, IEEE Trans. Circuits Syst. II, Express Briefs 54 (January (1)) (2007) 76–80.

- [15] R. Singh, Y. Audet, Y. Gagnon, Y. Savaria, E. Boulais, M. Meunier, A laser-trimmed rail-to-rail precision CMOS operational amplifier, IEEE Trans. Circuits Syst. II, Express Briefs 58 (February (2)) (2011) 75–79.

- [16] L. Moldovan, H.-H. Li, A rail-to-rail, constant gain, buffered op-amp for real time video applications, IEEE J. Solid-State Circuits 32 (February (2)) (1997)

- [17] T. Stockstad, H. Yoshizawa, A 0.9-V 0.5-µA rail-to-rail CMOS operational amplifier, IEEE J. Solid-State Circuits 37 (March (3)) (2002) 286–292.

- [18] J.-M. Carrillo, J.F.D. Carrillo, G. Torelli, J.-L. Ausin, Constant-gm constant-slew-rate high-bandwidth low-voltage rail-to-rail CMOS input stage for VLSI cell libraries, IEEE J. Solid-State Circuits 38 (August (8)) (2003) 1364–1372.

- [19] J.-M. Carrillo, G. Torelli, P.-A. Raquel, J.F.D. Carrillo, 1-V rail-to-rail CMOS OpAmp with improved bulk-driven input stage, IEEE J. Solid-State Circuits 42 (March (3)) (2007) 508–517.

- [20] M.-F. Snoeij, M.-V. Ivanov, A 36 V JFET-input bipolar operational amplifier with  $1 \mu V$ /°C maximum offset drift and -126 dB total harmonic distortion, in: Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, February 2011, pp. 248–250.

- [21] D. Bianchi, F. Quaglia, A. Mazzanti, F. Svelto, A 90Vpp 720 MHz GBW linear power amplifier for ultrasound imaging transmitters in BCD6-SOI, in: Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, February 2012, pp. 370–372.

- [22] M. Lemkin, A 200-V high-voltage amplifier using a parasitic field-oxide transistor for voltage feedback, IEEE J. Solid-State Circuits 38 (October (10)) (2003) 1730–1734.

- [23] K. Tripetch, A novel techniques for step down converter implemented by high voltage operational amplifier, in: Proceedings of the International Symposium on Power Electronics, Electrical Drives, Automation and Motion, June 2012, pp. 287–292.

- [24] C.-L. Chen, Y.-L. Wu, C.-Y. Juan, C.-C. Wang, High voltage operational amplifier and high voltage transceiver using 0.25 μm 60 V BCD process for battery management systems, in: Proceedings of the IC International Conference on Design & Technology, May 2013, pp. 97–100.